![]()

Типовые маршруты

Проверка корректности схемы

Построение маршрута по типовому маршруту возможно, если схема типового маршрута является корректной. Для того чтобы проверить, является ли схема корректной, необходимо выбрать пункт главного меню Сервис/Проверить схему. Также корректность схемы автоматически проверяется при её сохранении.

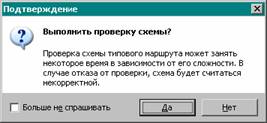

При большом количестве блоков проверка корректности схемы может занять длительное время. В этом случае при сохранении схемы выведется сообщение:

Для отмены проверки нужно нажать на кнопку Нет.

Для выполнения проверки нужно нажать на кнопку Да.

Схема является корректной, если она соответствует следующим условиям:

· блок «Начало» не должен иметь входящих соединений и должен иметь хотя бы одно исходящие соединение;

· блок «Конец» не должен иметь исходящих соединений и должен иметь хотя бы одно входящие соединение;

· все блоки, кроме блока «Начало», должны иметь хотя бы одно входящее соединение;

· должен существовать хотя бы один путь от блока «Начало» до блока «Конец»;

· для блоков «Задание» и «Уведомление» должен быть задан Исполнитель;

· в схемах свободных маршрутов не должно быть циклов;

· в жестких маршрутах вход в циклы может быть только через один и тот же блок. Например, если блоки А, Б и В образуют цикл А -> Б -> В -> А, то вход в этот цикл из других блоков схемы возможен, только через один из блоков цикла, например, А.;

Если схема не удовлетворяет условиям корректности, то появляется сообщение об ошибке «Схема маршрута содержит ошибки» и внизу редактора схем отображается панель ошибок (см. раздел «Панель ошибок»):

Для перехода к блоку, к которому относится ошибка, необходимо выполнить двойное нажатие левой кнопки мыши или нажать клавишу <Enter> на ошибке.

См. также:

· Описание;

· Панель «Свойства элементов»;

· Просмотр состояния выполнения задачи;

|

© 2009, Компания DIRECTUM

|

|

Отправить комментарий к этому разделу на

support@directum.ru

|